תהליך העיצוב של חומרה דיגיטלית השתנה באופן אינטנסיבי במהלך השנים האחרונות. לכן, ניתן ליישם מעגלים דיגיטליים קטנים באמצעות PALs ו- PLAs. נעשה שימוש בכל מכשיר ליישום מעגלים שונים שאינם זקוקים ליותר ממספר i / ps, o / ps ותנאי המוצר המוצעים בשבב הספציפי. שבבים אלה אינם מספיקים לגדלים צנועים למדי, בדרך כלל תומכים במספר הדדי של כניסות ויציאות של לא יותר מ 32. לצורך תכנון מעגלים אלה הזקוקים לכניסות ותפוקות רבות יותר, ניתן להיעזר ב- PLAs / PAL רבים או אחרת מסוג קלאסי יותר של שבב ניתן להשתמש בשם CPLD (התקן לוגיקה מורכב לתכנות). שבב CPLD כולל מספר בלוקי מעגל על שבב יחיד עם משאבי חיווט פנימיים לחיבור בלוקי המעגל. כל בלוק מעגל ניתן להשוואה ל- PLA או ל- PAL.

מהו מכשיר לוגי מורכב לתכנות?

ראשי התיבות של CPLD הם 'התקני לוגיקה מורכבים לתכנות', זה אחד סוג של מעגל משולב שמעצבי אפליקציות מתכננים ליישם חומרה דיגיטלית כמו טלפונים ניידים. אלה יכולים להתמודד עם עיצובים גבוהים ביודעין מאשר SPLDs (התקני לוגיקה פשוטים לתכנות), אך מציעים פחות היגיון מ- FPGA ( מערכי שער לתכנות בשטח CPLDs כוללים חסימות לוגיות רבות שכל אחת מהבלוקים כוללת 8-16 תאי מקרוצ'ל. מכיוון שכל בלוק לוגי מבצע פונקציה ספציפית, כל המיקרוצלים בבלוק לוגי מחוברים לחלוטין. בהתאם לשימוש, בלוקים אלה עשויים להיות מחוברים זה לזה או לא.

התקן לוגי מורכב לתכנות

ברוב ה- CPLDs (התקני לוגיקה מורכבים לתכנות) יש תאי מקרוצ'ר עם סכום של פונקציית לוגיקה ואלקטיבי FF (כפכף) . בהתאם לשבב, פונקציית הלוגיקה המשולבת תומכת בין 4 ל -16 מונחי מוצר עם מאוורר כולל. CPLDs נבדלים גם מבחינת רושמי משמרות ושערי לוגיקה. מסיבה זו, ניתן להשתמש ב- CPLDs עם מספר עצום של שערי לוגיקה במקום ב- FPGA. מפרט אחר של CPLD מסמל את מספר מונחי המוצר שמאקרוצ'ל יכול להשיג. מונחי מוצר הם תוצר של אותות דיגיטליים המבצעים פונקציית לוגיקה ספציפית.

CPLDs זמינים במספר טפסים של חבילות IC ומשפחות לוגיות. CPLDs נבדלים גם מבחינת מתח האספקה, זרם ההפעלה, זרם המתנה ופיזור החשמל. בנוסף, ניתן להשיג אותם עם כמויות שונות של זיכרון וסוגים שונים של תמיכה בזיכרון. בדרך כלל, הזיכרון מתבטא בסיביות / מגה ביט. תמיכה בזיכרון מורכבת מ- ROM, RAM ו- RAM עם יציאה כפולה. הוא כולל גם זיכרון CAM (זיכרון שניתן להתייחס אליו בתוכן) וכן זיכרון FIFO (ראשונה, ראשונה) וזיכרון LIFO (אחרון, אחרון).

ארכיטקטורה של מכשיר לוגי מורכב לתכנות

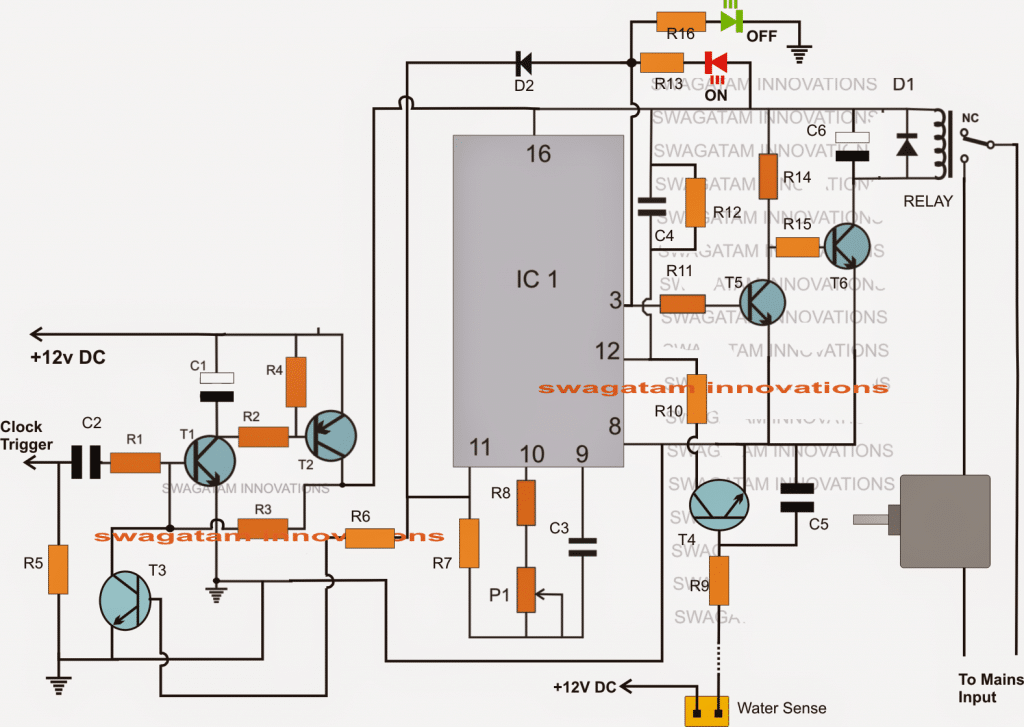

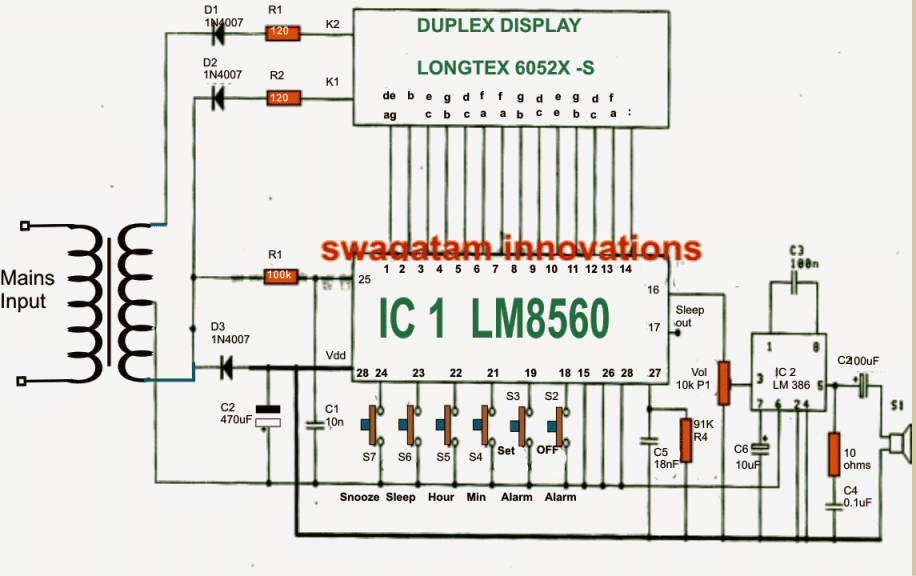

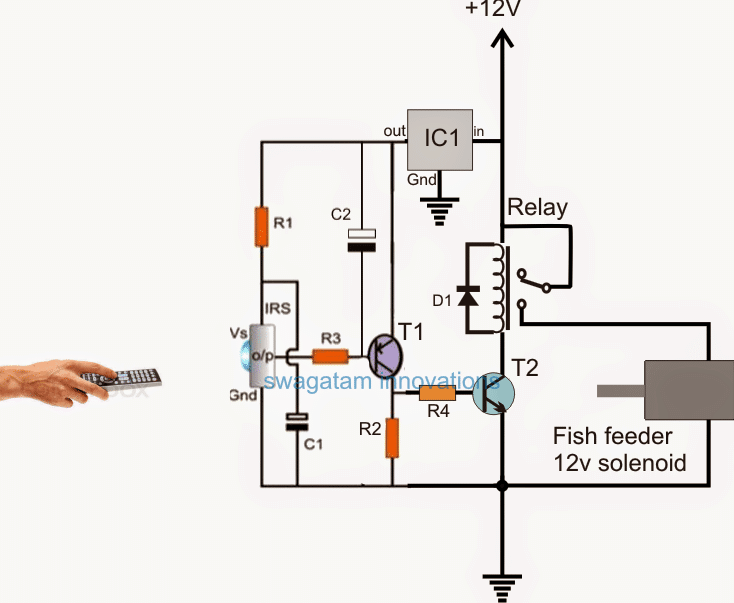

מכשיר לוגי לתכנות מורכב מורכב מקבוצת FBs (בלוקים פונקציונליים) ניתנים לתכנות. הכניסות והתפוקות של הבלוקים הפונקציונליים הללו מחוברות יחד באמצעות GIM (מטריצת חיבורים גלובלית). ניתן להגדיר מחדש את מטריצת הקישוריות הזו, כך שנוכל לשנות את המגעים בין הבלוקים הפונקציונליים. יהיו כמה בלוקי קלט ופלט המאפשרים לנו לאחד CPLD לעולם חיצוני. הארכיטקטורה של CPLD מוצגת להלן.

באופן כללי, ה- FB לתכנות נראה כמו מערך שערי לוגיקה , שם ניתן לתכנת מערך של AND שערים ושערי OR יציבים. אבל לכל יצרן יש את צורת החשיבה שלו לעצב את הגוש הפונקציונלי. ניתן למצוא O / p רשום על ידי הפעלת אותות המשוב שהושגו מיציאות השער OR.

CPLD אדריכלות

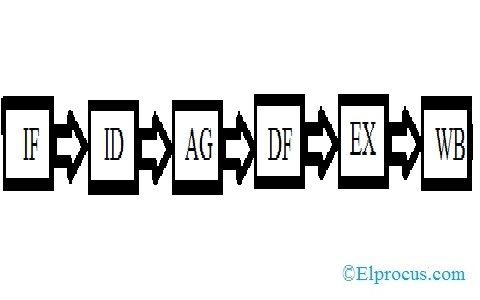

בתכנות CPLD, העיצוב מקודד תחילה בשפת Verilog או VHDL ברגע שהקוד (מדומה ומסונתז. במהלך הסינתזה נבחר ידנית מודל ה- CPLD (מכשיר היעד) ויוצר רשימת מיפוי מבוססת טכנולוגיה. רשימה זו יכולה להיות קרובה -התאמה לארכיטקטורת ה- CPLD האמיתית תוך שימוש בתהליך מקום ונתיב, בדרך כלל מושגת על ידי תוכנת המקום-והמסלול של חברת CPLD הקניינית. ואז המפעיל יבצע כמה תהליכי אישור. אם הכל טוב, הוא ישתמש ב- CPLD, אחרת הוא יסדר אותו מחדש.

סוגיות ארכיטקטורה של CPLD

כאשר בוחנים מכשיר לוגי מורכב לתכנות לשימוש בתכנון, ניתן לקחת בחשבון כמה סוגיות ארכיטקטורות הבאות

- טכנולוגיית התכנות

- יכולת חסימת הפונקציות

- יכולת הקלט / פלט

חלק מהמשפחות של CPLD מקמעונאים שונים כוללות

- משפחות Altera MAX 7000 ו- MAX 9000

- משפחות ATF ATF וטרקטורונים

- משפחת אס.פי.אס.אס.

- משפחת MACH של סריג (ואנטיס)

- משפחת Xilinx XC9500

משפחות CPLD

יישומים של CPLD

היישומים של CPLDs כוללים את הדברים הבאים

- התקני לוגיקה מורכבים הניתנים לתכנות הם אידיאליים ליישומי בקרה קריטיים עם ביצועים גבוהים.

- ניתן להשתמש ב- CPLD בעיצוב דיגיטלי לביצוע הפונקציות של מטעין האתחול

- CPLD משמש לטעינת נתוני התצורה של מערך שער לתכנות בשטח מזיכרון לא נדיף.

- בדרך כלל, אלה משמשים ביישומי עיצוב קטנים כמו פענוח כתובות

- CPLDs משמשים לעתים קרובות יישומים רבים כמו בהתקנים ניידים רגישים לעלות, המופעלים על ידי סוללות, בשל גודלם הנמוך והשימוש בהספק נמוך.

לפיכך, מדובר בסך הכל בארכיטקטורת התקנים לוגית מורכבת וניתנת לתכנות ויישומיה. אנו מקווים שיש לך הבנה טובה יותר של מושג זה. יתר על כן, כל שאלה בנוגע למושג זה או ליישום פרויקטים חשמליים ואלקטרוניים אנא הוסף את הצעותיך החשובות על ידי תגובה בקטע התגובות למטה. הנה שאלה עבורך, מה ההבדל בין CPLD ל- FPGA?

נקודות זיכוי:

- CPLD ויקימדיה

- אדריכלות של CPLD slidesharecdn