ישנם סוגים שונים של משפחות לוגיות זמינות המשמשות בתכנון מעגלים לוגיים דיגיטליים; לוגיקה טרנזיסטור נגד (RTL), לוגיקה משותפת של פולט (ECL), לוגיקה טרנזיסטורית של דיודה (DTL), לוגיקה של מוליכים למחצה מתכת תחמוצת משלימה (CMOS), ו לוגיקה טרנזיסטור-טרנזיסטור (TTL) . מתוך משפחות לוגיקה אלו, משפחת הלוגיקה DTL הייתה בשימוש נפוץ לפני שנות ה-60 וה-70 כדי להחליף משפחות לוגיות מתקדמות יותר כמו CMOS ו-TTL. לוגיקה דיודה-טרנזיסטור היא מחלקה של מעגלים דיגיטליים שתוכנן עם דיודות וטרנזיסטורים. אז השילוב של דיודות וטרנזיסטורים מאפשר ליצור פונקציות לוגיות מורכבות עם רכיבים קטנים למדי. מאמר זה מספק מידע קצר על לוגיקה של טרנזיסטור DTL או דיודה והיישומים שלה.

מהי לוגיקה טרנזיסטור דיודה?

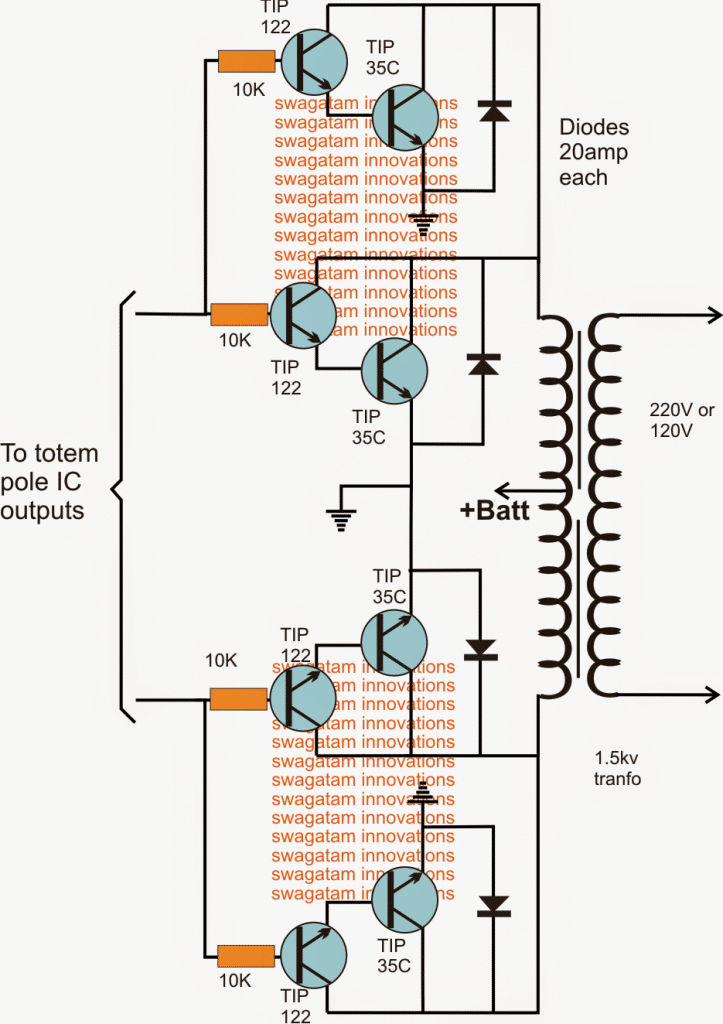

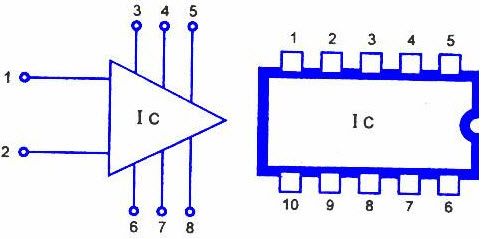

לוגיקה טרנזיסטור דיודה היא מעגל לוגי השייך למשפחת הלוגיקה הדיגיטלית המשמשת ליצירת מעגלים דיגיטליים. מעגל זה יכול להיות מתוכנן עם דיודות וטרנזיסטורים שבהם נעשה שימוש בדיודות בצד הקלט ובטרנזיסטורים בצד המוצא, ולכן זה ידוע בשם DTL. DTL הוא סוג ספציפי של מעגל המשמש באלקטרוניקה דיגיטלית נוכחית לעיבוד אותות חשמליים.

במעגל לוגי זה, דיודות שימושיות בביצוע פונקציות לוגיות, בעוד טרנזיסטורים משמשים לביצוע פונקציות ההגברה. ל-DTL יתרונות רבים בהשוואה ל נַגָד לוגיקה טרנזיסטור כמו; ערכי המניפה הגבוהים יותר ושולי הרעש הגבוהים ולכן, DTL מוחלף במשפחת RTL. ה מאפיינים של לוגיקה טרנזיסטור דיודה כוללים בעיקר; חסר תרבות דיגיטלית, אסטרטג דיגיטלי, ארכיטקט דיגיטלי, זריז ביותר ארגוני, מרכז לקוחות, עורך דין נתונים, מעצב מקום עבודה דיגיטלי וממטב תהליכים עסקיים.

מעגל לוגי טרנזיסטור דיודה

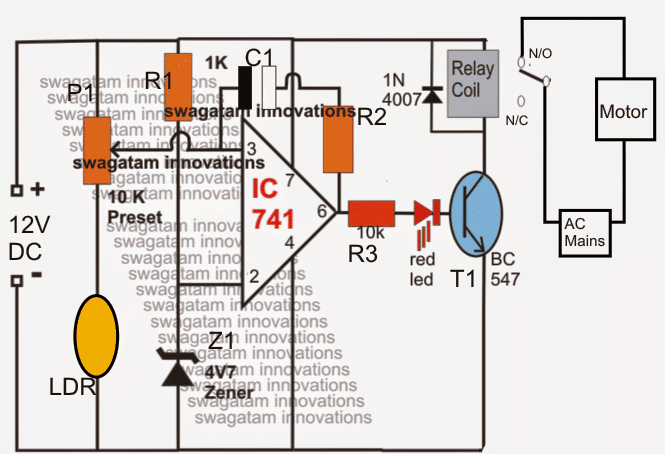

מעגל הלוגי טרנזיסטור דיודה מוצג להלן. זהו מעגל שער NAND לוגי של טרנזיסטור דיודה עם שתי כניסות. מעגל זה מתוכנן עם שתי דיודות וטרנזיסטור כאשר שתי דיודות מסומנות ב-D1, ו-D2 והנגד מסומן ב-R1 המהווה את צד הקלט של המעגל הלוגי. תצורת טרנזיסטור Q1 CE ונגד R2 מהווים את צד הפלט. הקבל 'C1' במעגל זה משמש כדי לתת זרם הילוך יתר לאורך זמן המיתוג וזה מקטין את זמן המיתוג לרמה מסוימת.

לוגיקה של טרנזיסטור דיודה עובדת

בכל פעם ששני הכניסות של המעגלים A ו-B נמוכים, אז גם דיודות D1 ו-D2 יהפכו מוטות קדימה, ולכן דיודות אלו יובילו בכיוון קדימה. לכן אספקת הזרם בגלל אספקת המתח (+VCC = 5V) תספק ל-GND לאורך כל הנגד R1 ושתי הדיודות. אספקת המתח מצטמצמת בתוך הנגד R1 ולא יספיק להפעיל את הטרנזיסטור Q1, ולכן הטרנזיסטור Q1 יהיה במצב ניתוק. אז, ה-o/p במסוף 'Y' יהיה לוגי 1 או ערך גבוה.

כאשר כל אחת מהכניסות היא LOW, אז הדיודה המתאימה תהיה מוטה קדימה ולכן פעולה דומה תתרחש. מכיוון שכל אחת מהדיודות הללו מוטה קדימה, אז זרם יסופק לאדמה לאורך כל הדיודה המוטה קדימה, ולכן הטרנזיסטור 'Q1' יהיה במצב חיתוך, כך שהמוצא במסוף 'Y' יהיה גבוה או הגיוני 1.

בכל פעם ששתי כניסות A ו-B גבוהות אז שתי הדיודות יהיו מוטות לאחור, ולכן שתי הדיודות לא יובילו. אז במצב זה, המתח מאספקת +VCC יהיה מספיק כדי להניע את הטרנזיסטור Q1 למצב הולכה.

לכן הטרנזיסטור מוליך לאורך מסופי הפולט והאספן. המתח כולו מופחת בתוך הנגד 'R2' והיציאה במסוף 'Y' תהיה בעלת o/p נמוכה ונחשבת לנמוכה או לוגית 0.

שולחן האמת

טבלת האמת של DTL מוצגת להלן.

|

א |

ב | ו |

|

0 |

0 | 1 |

|

0 |

1 |

1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

עיכוב ההפצה הלוגית של טרנזיסטור הדיודה הוא די גדול. בכל פעם שכל הכניסות הן לוגיות גבוהות אז הטרנזיסטור יכנס להצטברות רוויה וטעינה באזור הבסיס. בכל פעם שקלט אחד נמוך, יש להסיר את המטען הזה, ולשנות את זמן ההתפשטות. כדי להאיץ את הלוגיקה של טרנזיסטור הדיודה בטכניקה אחת היא על ידי הוספת קבל על פני הנגד R3. כאן, קבל זה מסייע בכיבוי הטרנזיסטור על ידי ביטול המטען המצטבר במסוף הבסיס. הקבל במעגל זה מסייע גם בהפעלת הטרנזיסטור באמצעות שיפור כונן הבסיס הראשון.

לוגיקה טרנזיסטור דיודה שונה

שער ה-DTL NAND שהשתנה מוצג להלן. קשה מאוד לייצר באופן כלכלי את הערכים הגדולים של רכיבי הנגדים והקבלים על IC. אז ניתן לשנות את מעגל השער DTL NAND הבא ליישום IC פשוט על ידי ביטול הקבל C1, הפחתת ערכי הנגד ושימוש טרנזיסטורים ודיודות בכל מקום שניתן להשיג. מעגל שונה זה פשוט משתמש באספקה חיובית אחת ומעגל זה כולל שלב כניסה עם דיודות D1 ו-D2, נגד R3 ושער AND אשר עוקבים אחריו דרך מהפך טרנזיסטורי.

עובד

הפעולה של מעגל זה היא שלמעגל זה יש שני מסופי כניסה A ו-B, ומתחי כניסה כמו A & B יכולים להיות גבוהים או נמוכים.

אם שתי הכניסות A ו-B נמוכות או לוגיות 0, אז שתי הדיודות יעברו מוטות קדימה, ולכן הפוטנציאל ב-'M' הוא מפל המתח של דיודה אחת שהיא 0.7 V. אם כי כדי להניע את הטרנזיסטור 'Q' להולכה , אז אנחנו צריכים 2.1 V כדי להטות קדימה את הדיודות D3, D4 ואת צומת BE של הטרנזיסטור 'Q', לפיכך טרנזיסטור זה הוא החיתוך ומספק פלט Y = 1

Y = Vcc = Logic 1 ועבור A = B = 0, ה-Y = 1 או High.

אם כל אחת מהכניסות A או B נמוכה, אז כל אחת מהכניסות יכולה להיות מחוברת ל-GND עם כל טרמינל מחובר ל-+Vcc, הדיודה המקבילה תוביל, וטרנזיסטור VM ≅ 0.7 V & Q ינותק , וספק פלט 'Y' = 1 או לוגי גבוה.

אם A = 0 & B =1 (או) אם A = 1 & B = 0, אז פלט Y = 1 או HIGH.

אם שתי כניסות כמו A & B הן HIGH ושניהם A & B מחוברים פשוט ל-+Vcc, אז שתי דיודות D1 ו-D2 יהיו מבוססות הפוך והן אינן מוליכות. דיודות D3 ו-D4 מוטות קדימה והזרם במסוף הבסיס מסופק פשוט לטרנזיסטור Q דרך Rd, D3 ו-D4. ניתן להניע את הטרנזיסטור לרוויה ומתח ה-o/p יהיה מתח נמוך.

עבור A = B = 1, הפלט Y = 0 או LOW.

היישומים של DTL שונה כוללים את הדברים הבאים.

יציאת מאוורר גדולה יותר אפשרית עקב שערים הבאים בעלי עכבה גבוהה עם מצב ההיגיון HIGH. למעגל זה חסינות רעש מעולה. השימוש במספר דיודות במקום נגדים וקבלים יהפוך את המעגל הזה לחסכוני מאוד בצורת המעגל המשולב.

Diode Transistor Logic NOR Gate

שער NOR לוגיקה של טרנזיסטור דיודה מעוצב בדומה לשער DTL NAND עם שער DRL OR עם מהפך טרנזיסטור. ניתן לעצב מעגלי DTL NOR בצורה אלגנטית יותר על ידי שילוב פשוט של ממירי DTL שונים באמצעות פלט משותף. באופן זה, ניתן לאחד מספר ממירים כדי לתת את הכניסות הדרושות לשער NOR.

מעגל זה יכול להיות מתוכנן עם הרכיבים של מעגל DTL Inverter מלבד ספק כוח ושני 4.7 K נגדים , 1N914 או 1N4148 דיודות סיליקון. חבר את המעגל לפי המעגל שמוצג להלן.

עובד

לאחר ביצוע החיבורים, צריך לספק את אספקת החשמל למעגל. לאחר מכן, החל ארבעה שילובי קלט אפשריים ב-A ו-B מאספקת הכוח עם מתג טבילה. כעת עבור כל שילוב קלט, צריך לרשום את המצב הלוגי של הפלט 'Q' כפי שמוצג ב- לד & להקליט את הפלט הזה. השווה את התוצאות עם פעולת שער NOR. לאחר שתסיים את התצפיות שלך, כבה את אספקת החשמל.

|

א |

ב |

Y = (A+B)' |

|

0 |

0 | 1 |

|

0 |

1 | 0 |

| 1 | 0 |

0 |

| 1 | 1 |

0 |

דיודה טרנזיסטור לוגיקה ושער

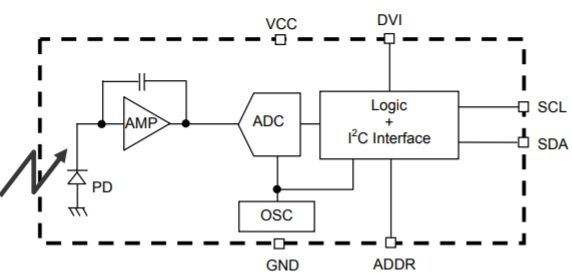

הלוגיקה ושער הטרנזיסטור של הדיודה מוצגים להלן. במעגל זה, ההיגיון קובע כמו; 1 ו-0 נלקחים כהיגיון חיובי +5V ו-0V בהתאם.

בכל פעם שכניסה כלשהי מ-A1, A2 (או) A3 נמצאת במצב לוגי נמוך, אז הדיודה שמחוברת לכניסה זו תהיה בהטיה קדימה לאחר מכן, הטרנזיסטור ייכנס למנותק והמוצא יהיה LOW או לוגי 0 באופן דומה, אם כל שלושת הכניסות נמצאות בלוגיקה 1 אז אף אחת מהדיודות לא מוליכה והטרנזיסטור מוליכה בכבדות. לאחר מכן, הטרנזיסטור רווי והפלט יהיה HIGH או לוגי 1.

טבלת האמת של הלוגיקה והשער של טרנזיסטור דיודה מוצגת להלן.

|

A1 |

A2 | A3 |

Y = A.B |

|

0 |

0 | 0 | 0 |

|

0 |

0 | 1 | 0 |

|

0 |

1 | 0 |

0 |

| 0 | 1 | 1 |

0 |

|

1 |

0 | 0 | 0 |

|

1 |

0 | 1 |

0 |

| 1 | 1 | 0 |

0 |

| 1 | 1 | 1 |

1 |

השוואה בין DTL, TTL ו-RTL

ההבדלים בין DTL, TTL ו-RTL נדונים להלן.

| DTL | TTL |

RTL |

| המונח DTL מייצג דיודה-טרנזיסטור לוגיקה. | המונח TTL מייצג טרנזיסטור-טרנזיסטור לוגיקה. | המונח RTL הוא ראשי תיבות של Resistor-Transistor Logic. |

| ב-DTL, השערים הלוגיים מתוכננים עם דיודות צומת PN וטרנזיסטורים. | ב-TTL, שערים לוגיים מתוכננים עם BJTs.

|

ב-RTL, השערים הלוגיים מתוכננים עם הנגד והטרנזיסטור. |

| ב-DTL, דיודות משמשות כרכיבי i/p וטרנזיסטורים משמשים כרכיבי o/p. | ב-TTL, טרנזיסטור אחד משמש להגברה ואילו טרנזיסטור אחר משמש למטרות מיתוג. | הנגד ב-RTL משמש כרכיב i/p והטרנזיסטור משמש כרכיב o/p |

| תגובת DTL טובה יותר בהשוואה ל-RTL. | תגובת TTL טובה בהרבה מ-DTL ו-RTL. | תגובת RTL איטית. |

| אובדן החשמל נמוך. | יש לו אובדן חשמל נמוך מאוד. | אובדן החשמל גבוה. |

| בנייתו מורכבת. | הבנייה שלו פשוטה מאוד. | הבנייה שלו פשוטה. |

| DTL minimum fanout הוא 8. | ה-TTL המינימום אוהד הוא 10. | המינימום הפאנאוט של RTL הוא 5. |

| פיזור הספק עבור כל שער הוא בדרך כלל 8 עד 12 mW. | פיזור הספק עבור כל שער הוא בדרך כלל 12 עד 22 mW. | פיזור הספק עבור כל שער הוא בדרך כלל 12 mW. |

| חסינות הרעש שלו טובה. | חסינות הרעש שלו טובה מאוד. | חסינות הרעש שלו בינונית. |

| עיכוב ההתפשטות האופייני שלו לשער הוא 30 ns. | עיכוב ההתפשטות האופייני שלו עבור השער הוא 12 עד 6 ns. | עיכוב ההתפשטות האופייני שלו לשער הוא 12 ns. |

| קצב השעון שלו הוא 12 עד 30 מגה-הרץ. | קצב השעון שלו הוא 15 עד 60 מגה-הרץ. | קצב השעון שלו הוא 8 מגה-הרץ. |

| יש לו מספר די גבוה של פונקציות. | יש לו מספר גבוה מאוד של פונקציות. | יש לו מספר רב של פונקציות. |

| לוגיקה DTL משמשת במיתוג ומעגלים דיגיטליים בסיסיים. | לוגיקה TTL משמשת במעגלים דיגיטליים מודרניים ומעגלים משולבים. | RTL משמש במחשבים ישנים. |

יתרונות

היתרונות של מעגל לוגי טרנזיסטור דיודה כוללים את הדברים הבאים.

- מהירות המעבר של DTL מהירה יותר בהשוואה ל-RTL.

- השימוש בדיודות בתוך מעגלי DTL הופך אותם לזולים יותר מכיוון שהייצור של דיודות על ICs הוא פשוט יותר בהשוואה לנגדים וקבלים.

- אובדן החשמל בתוך מעגלי DTL נמוך מאוד.

- למעגלי DTL יש מהירויות מיתוג מהירות יותר.

- ל-DTL יש מאוורר גדול יותר ושולי רעש משופרים.

ה חסרונות של מעגלים לוגיים טרנזיסטור דיודה כלול את הבאים.

- ל-DTL מהירות פעולה נמוכה בהשוואה ל-TTL.

- יש לו עיכוב התפשטות שער גדול במיוחד.

- עבור קלט גבוה, הפלט של DTL נכנס לרוויה.

- הוא מייצר חום לאורך כל הפעולה.

יישומים

ה יישומים של לוגיקה טרנזיסטור דיודה כלול את הבאים.

- Diode- Transistor Logic משמש לתכנון וייצור מעגלים דיגיטליים היכן שערים לוגיים השתמש בדיודות בשלב הקלט וב-BJTs בשלב הפלט.

- DTL הוא סוג ספציפי של מעגל המשמש באלקטרוניקה דיגיטלית נוכחית לעיבוד אותות חשמליים.

- DTL משמש לייצור מעגלים לוגיים פשוטים.

לפיכך, זהו סקירה כללית של לוגיקה טרנזיסטור דיודה , מעגל, עבודה, יתרונות, חסרונות ויישומים. מעגלי DTL מורכבים יותר בהשוואה למעגלי RTL, אך ההיגיון הזה שינה את RTL בגלל יכולת ה-FAN OUT המעולה שלו ושולי הרעש המשופרים שלו, אך ל-DTL יש מהירות איטית. הנה שאלה בשבילך, מה זה RTL?