בחיי היום יום שלנו אנו נתקלים בסוגים שונים של גאדג'טים אלקטרוניים. אחת הטכנולוגיות שהביאו מהפכה בייצור אלקטרוניקה היא ' מעגל משולב '. טכנולוגיה זו הקטינה את גודל המוצרים האלקטרוניים על ידי הגדלת הצפיפות של שערים לוגיים לכל שבב. כיום יש לנו סוגים ותצורות שונות של IC. כפי שאנו מתבוננים בסביבתנו אנו מוצאים כי ניתן להשתמש בתמ'כים מסוימים רק ליישום ספציפי אחד ואילו ניתן לתכנת מחדש את מכשירי IC מסוימים ולהשתמש בהם ליישומים שונים. סוגים אלה של מכשירי IC נקראים ASIC. אבל במה הם נבדלים? איך אפשר לתכנת אותם מחדש? מדוע לא ניתן לתכנת מחדש מכשירי IC מסוימים? קפץ על מנת למצוא תשובות לשאלות אלה.

מהו ASIC (מעגל משולב יישום ספציפי)?

הטופס המלא של ASIC הוא מעגל משולב ספציפי ליישום. מעגלים אלה הם ספציפיים ליישומים. ICs תפור במיוחד עבור יישום מסוים. אלה מתוכננים בדרך כלל מרמת שורש בהתבסס על דרישת היישום המסוים. חלק מהבסיסים דוגמאות למעגלים משולבים ספציפיים ליישומים הם שבבים המשמשים לצעצועים, השבב המשמש לממשק זיכרון ומעבד וכו '... ניתן להשתמש בשבבים אלה רק לאפליקציה אחת שעבורה אלה מיועדים. יש להניח כי אלה סוגי ICs מועדפים רק עבור מוצרים עם ריצת ייצור גדולה. מכיוון ש- ASIC מתוכננים מרמת השורש יש להם עלות גבוהה ומומלצים רק להפקות בנפח גבוה.

היתרון העיקרי של ASIC הוא צמצום גודל השבב שכן מספר גדול של יחידות פונקציונליות של מעגל בנויות על גבי שבב יחיד. ASIC מודרני כולל בדרך כלל 32 סיביות מיקרו - מעבד , חסימות זיכרון, מעגלי רשת וכו '... סוג כזה של ASIC נקרא מערכת על שבב . עם ההתפתחות בטכנולוגיית הייצור והמחקר המוגבר בשיטות העיצוב מפותחים ASIC עם רמות התאמה אישית שונות.

סוגי ASIC

רכיבי ASIC מסווגים על פי כמות ההתאמה האישית שמותר למתכנת לבצע על שבב.

סוגי ASIC

בהתאמה אישית מלאה

בסוג זה של עיצוב כל תאי ההיגיון מותאמים ליישום ספציפי. כלומר. על המעצב להכין במיוחד את תאי ההיגיון למעגלים. כל שכבות המסכה לחיבור הדדי מותאמות אישית. כך שמתכנת לא יכול לשנות את חיבורי הגומלין של השבב ותוך כדי התכנות הוא צריך להיות מודע לפריסת המעגל.

אחת הדוגמאות הטובות ביותר ל- ASIC בהתאמה אישית מלאה היא מעבד. סוג זה של התאמה אישית מאפשר למעצבים לבנות מעגלים אנלוגיים שונים, תאי זיכרון מותאמים או מבנים מכניים על גבי IC יחיד. ASIC זה יקר מאוד זמן לייצור ועיצוב. הזמן שלוקח לתכנן את מכשירי ה- IC הללו הוא כשמונה שבועות.

אלה מיועדים בדרך כלל ליישומים ברמה גבוהה. ביצועים מרביים, שטח ממוזער וגמישות גבוהה ביותר הם המאפיינים העיקריים של עיצוב מותאם אישית מלא. בסופו של דבר, הסיכון הוא גבוה בעיצוב מכיוון שתאי ההיגיון, הנגד וכו '... אלמנטים במעגלים המשמשים אינם מבוצעים מחדש.

חצי מותאם אישית

בסוג זה של תאים לוגיים תכנוניים נלקחים מספריות סטנדרטיות. כלומר. הם לא מיוצרים בעבודת יד כמו בתכנון מלא בהתאמה אישית. מסכות מסוימות מותאמות אישית ואילו חלקן נלקחות מהספריה שתוכננה מראש. בהתבסס על סוג תאי ההיגיון שנלקחו מהספרייה וכמות ההתאמה האישית המותרת לחיבורים הדדיים מחולקים ASIC אלה לשני סוגים - ASIC מבוסס תא סטנדרטי ו- ASIC מבוסס שער מערך.

1). ASIC סטנדרטי מבוסס תאים

כדי להכיר את ה- IC תחילה, נבין מה עומדת ספריית תאים סטנדרטית. חלק מתאי ההיגיון כגון AND שערים, או שערים , מרבבים, כפכפים מעוצבים מראש על ידי מעצבים המשתמשים בתצורות שונות, מתוקננים ומאוחסנים בצורה של ספרייה. אוסף זה ידוע כספריית תאים סטנדרטית.

ASIC סטנדרטי מבוסס תאים

בתאים סטנדרטיים מבוססי תאים, ASIC מספריות סטנדרטיות אלה משתמשים. על שבב ASIC אזור התא הסטנדרטי או הבלוק הגמיש מורכבים מתאים סטנדרטיים המסודרים בצורת שורות. יחד עם הבלוקים הגמישים הללו משתמשים בתאים מגה כמו מיקרו-בקרים או אפילו מיקרו-מעבדים. תאי מגה אלה ידועים גם בשם פונקציות מגה, פקודות מאקרו ברמת המערכת, בלוקים קבועים, בלוקים סטנדרטיים פונקציונליים.

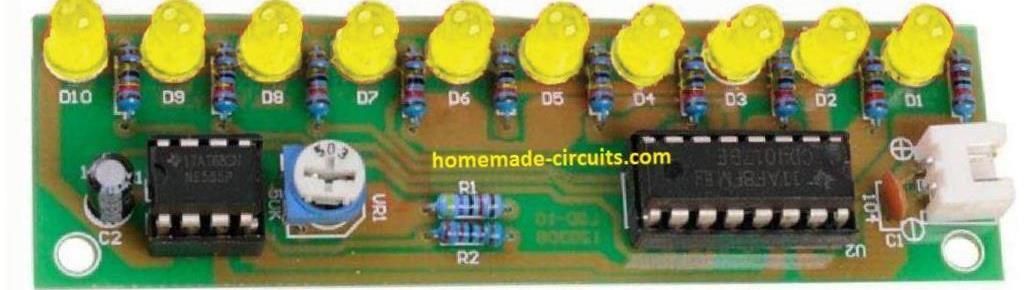

הדמות לעיל מייצגת ASIC תא סטנדרטי עם שטח תא סטנדרטי יחיד וארבעה בלוקים קבועים. שכבות מסכה מותאמות אישית. כאן המעצב יכול למקם תאים סטנדרטיים בכל מקום על המשטח. אלה ידועים גם בשם C-BIC.

2). שער מערך מבוסס ASIC

סוג זה של ASIC מותאם אישית למחצה הגדירו מראש טרנזיסטורים על רקיק הסיליקון. כלומר. המעצב אינו יכול לשנות את מיקום הטרנזיסטורים הנמצאים במת. מערך בסיס הוא התבנית המוגדרת מראש של מערך השער ותא הבסיס הוא התא החוזר הקטן ביותר במערך הבסיס.

על המעצב מוטלת האחריות לשנות את קשרי הגומלין בין הטרנזיסטורים באמצעות שכבות המתכת הראשונות של המשטח. המעצב בוחר מתוך ספריית מערך השערים. אלה נקראים לעתים קרובות כמו מערך שערים מסוכים. ASIC מבוסס שער מערך הוא משלושה סוגים. הם מערך שערים מתועלים, מערך שערים פחות ערוצי ומערך שער מובנה.

א). מערך שערים ערוצים

בסוג זה של מערך שערים, נותר שטח חיווט בין שורות טרנזיסטורים. אלה דומים ל- CBIC מכיוון שנותר מקום לחיבור הדדי בין בלוקים, אך בשורות תעלות מערך שערים קבועים בגובה ואילו ב- CBIC ניתן להתאים את החלל הזה.

מערך שערים מתועלים

חלק מהמאפיינים העיקריים של מערך שער זה הם - מערך שער זה משתמש ברווחים מוגדרים מראש בין שורות לצורך חיבור הדדי. זמן הייצור הוא יומיים עד שבועיים.

ב). מערך שער פחות בערוץ

לא נותר מקום פנוי לניתוב בין שורות תאים כפי שנראה במערך השער המתועל. כאן ניתוב נעשה מעל תאי מערך השער שכן אנו יכולים להתאים אישית את החיבור בין המתכת 1 לטרנזיסטורים. לצורך ניתוב אנו משאירים את הטרנזיסטורים מונחים בדרך הניתוב ללא שימוש. זמן ההובלה לייצור הוא כשבועיים.

מערך שער פחות בערוץ

ג). מערך שערים מובנים

לסוג זה של מערך שערים יש בלוק מוטבע יחד עם שורות מערך שערים כפי שנראה לעיל. למערך שערים מובנים יעילות שטח גבוהה יותר של CBIC. כמו מערך שערים עם מסיכות, גם בעלות נמוכה יותר ומהפך מהיר יותר. כאן הגודל הקבוע של הפונקציה המוטמעת מהווה מגבלה על מערך השערים המובנים. לדוגמא, האם מערך שער זה מכיל שטח השמור לבקר 32k סיביות אך אם ביישום אנו נדרשים רק אזור לבקר 16k סיביות השטח הנותר מתבזבז. לכל מערך השער זמן אספקה של יומיים עד שבועיים ו לכולם חיבור אינטראקטיבי בהתאמה אישית.

מערך שערים מובנים

ASIC לתכנות

ישנם שני סוגים של ASIC לתכנות. הם PLD ו- FPGA

PLDs (התקני לוגיקה ניתנים לתכנות)

אלה התאים הסטנדרטיים הזמינים בקלות. אנו יכולים לתכנת PLD להתאמה אישית של חלק מהיישום, ולכן הם נחשבים כ- ASIC. אנו יכולים להשתמש בשיטות ותוכנות שונות כדי לתכנת PLD. אלה מכילים מטריצה רגילה של תאי לוגיקה בדרך כלל לוגיקה של מערך לתכנות יחד עם כפכפים או תפסים. כאן קיימים קשרי גומלין כחסימה גדולה אחת.

PROM הוא דוגמה נפוצה ל- IC זה. EPROM משתמש בטרנזיסטורים של MOS כחיבור מקושר ולכן על ידי הפעלת מתח גבוה נוכל לתכנת אותו. ל- PLD אין תאי לוגיקה מותאמים אישית או קישוריות הדדית. אלה יש תפנית מהירה של עיצוב.

התקנים לוגיים ניתנים לתכנות

FPGAs (מערך שערים לתכנות בשטח)

היכן של- PLD יש לוגיקה של מערך לתכנות כתאי לוגיקה FPGA יש סידור דמוי מערך שער. PLD הם קטנים יותר ופחות מורכבים מ- FPGA. בשל הגמישות והמאפיינים שלה, FPGA מחליף TTL במערכות מיקרואלקטרוניות. המהפך העיצובי הוא רק כמה שעות.

מערך שערים לתכנות בשטח

הליבה מורכבת מתאי לוגיקה בסיסיים הניתנים לתכנות שיכולים לבצע את שניהם שילוב ו לוגיקה עוקבת . אנו יכולים לתכנת תאי לוגיקה ולהתחבר באמצעות כמה שיטות. תאי לוגיקה בסיסיים מוקפים במטריצה של חיבורי אינטראקציה הניתנים לתכנות והליבה מוקפת בתאי קלט / פלט לתכנות.

FPGA כולל בדרך כלל בלוקים לוגיים הניתנים להגדרה, בלוקי קלט / פלט ניתנים להגדרה, חיבורים ניתנים לתכנות, מעגלי שעון, ALU, זיכרון, מפענחים.

ראינו סוגים שונים של ASIC זמינים. עכשיו בואו נבין מתי כל ההתאמות האישיות והחיבורים האלו נעשות במהלך הייצור.

זרימת תכנון מעגל משולב יישומי (ASIC) ספציפי ליישום

תכנון ASIC מתבצע בצורה צעד אחר צעד. סדר צעדים זה מכונה עיצוב ASIC זְרִימָה. שלבי זרימת התכנון ניתנים בתרשים הזרימה להלן.

זרימת עיצוב ASIC

כניסה לעיצוב: בשלב זה המיקרו-ארכיטקטורה של העיצוב מיושמת באמצעות שפות לתיאור חומרה כגון VHDL, Verilog ו- System Verilog.

סינתזה לוגית: בשלב זה מכינים באמצעות רשת HDL רשימה של תאים לוגיים לשימוש, סוגי חיבורים וכל שאר החלקים הנדרשים ליישום.

מחיצת מערכת: בשלב זה אנו מחלקים את המתה בגודל הגדול לחתיכות בגודל ASIC.

סימולציה לפני פריסה: בשלב זה נעשית בדיקת סימולציה כדי לבדוק אם העיצוב מכיל שגיאות כלשהן.

תכנון קומה: בשלב זה מסודרים על השבב בלוקים של netlist.

מיקום: בשלב זה נקבע מיקום של תאים בתוך הבלוק.

ניתוב: בשלב זה מציירים חיבורים בין בלוקים לתאים. מיצוי: בשלב זה אנו קובעים את המאפיינים החשמליים כמו ערך התנגדות וערך הקיבול של חיבור מקושר.

סימולציה לאחר פריסה: לפני הגשת המודל לייצור נעשה סימולציה זו כדי לבדוק האם המערכת מתפקדת כהלכה יחד עם עומס של חיבור מקושר.

דוגמאות ל- ASIC

לאחר שהכרנו את המאפיינים השונים של ASIC, הבה נראה לנו כמה דוגמאות ל- ASIC.

ASIC סטנדרטי מבוסס תאים: LCB 300k, 500k מחברת LSI Logic, SIG1, 2, 3 משפחות מ- ABB Hafo Inc., GCS90K של GCS Plessey.

מוצרי שער מערכים: AUA20K מהאריס סמיקונדקטור, SCX6Bxx ממשקאות מוליכים למחצה, משפחות TGC / TEC מטקסס אינסטרומנטס.

מוצרי PLD: משפחת PAL של מכשירי מיקרו מתקדמים, משפחת GAL מבית פיליפס סמיקונדקטורס, XC7300 ו- EPLD מבית XILINX.

מוצרי FPGA: סדרות XC2000, XC3000, XC4000, XC5000 מבית XILINX, pASIC1 של QuickLogic, MAX5000 מבית Altera.

יישומי ASIC

הייחודיות של ASIC חוללה מהפכה באופן ייצור האלקטרוניקה. אלה הפחיתו את גדלי המות תוך הגדלת הצפיפות של שערים לוגיים לכל שבב. בדרך כלל מעדיפים ASIC ליישומים ברמה גבוהה. שבב ASIC משמש ליבות IP עבור לוויינים, ייצור ROM, מיקרו-בקר וסוגים שונים של יישומים בתחום הרפואה והמחקר. אחת היישומים הטרנדיים של ASIC היא BITCOIN MINER.

כורה ביטקוין

כריית מטבע קריפטוגרפי דורשת כוח גדול יותר וחומרה מהירה. מעבד למטרות כלליות אינו יכול לספק יכולת מחשוב כה גבוהה במהירות גבוהה. כורי ביטקוין של ASIC הם שבבים המובנים בלוחות אם שעוצבו במיוחד ספקי כוח , בנוי ליחידה אחת. זו חומרה שתוכננה בכוונה עד לרמת השבב לכריית ביטקוין. יחידות אלה יכולות לבצע אלגוריתם של מטבע יחיד בלבד. ככל הנראה עבור סוג אחר של מטבע קריפטוגרפי, אנו דורשים כורה אחר.

יתרונות וחסרונות של ASIC

ה היתרונות של ASIC כלול את הבאים.

- הגודל הקטן של ASIC הופך אותה לבחירה גבוהה עבור מערכות גדולות ומתוחכמות.

- כמספר גדול של מעגלים הבנויים על גבי שבב יחיד, הדבר גורם ליישומים מהירים.

- ל- ASIC צריכת חשמל נמוכה.

- מכיוון שהם המערכת שבב, המעגלים נמצאים זה לצד זה. לכן, יש צורך בניתוב מינימלי ביותר לחיבור מעגלים שונים.

- ל- ASIC אין בעיות תזמון ותצורה לאחר הייצור.

ה חסרונות של ASIC כלול את הבאים.

- מכיוון שמדובר בשבבים מותאמים אישית הם מספקים גמישות נמוכה לתכנות.

- מכיוון שצריך לעצב את השבבים הללו מרמת השורש, הם עלות גבוהה ליחידה.

- ל- ASIC זמן רב יותר לשולי השוק.

ASIC לעומת FPGA

ההבדל בין ASIC ו- FPGA כולל את הדברים הבאים.

ASIC | FPGA |

| לא ניתן לתכנות מחדש | ניתן לתכנות מחדש |

| מועדף להפקות בנפח גבוה | מועדף להפקות בנפח נמוך |

| אלה הם יישומים ספציפיים | משמש כאבות טיפוס של מערכת |

| חסכוני באנרגיה דורש פחות כוח | פחות חסכוני באנרגיה דורש יותר כוח |

| מדובר במעגלים קבועים שלא ניתן לשדרג מעת לעת. | מתאים מאוד ליישומים שבהם יש לשדרג את המעגל מעת לעת כגון שבבי טלפון סלולרי, תחנות בסיס וכו ' |

לפיכך, זה הכל על סקירה כללית של מעגל משולב ספציפי ליישום . המצאת ASIC גרמה לשינוי אדיר באופן השימוש באלקטרוניקה. אנו משתמשים ב- ASIC בחיי היומיום שלנו בצורה של יישומים שונים. באילו יישומים של ASIC נתקלת? עם איזה סוג של ASIC עבדת?