באופן כללי, החסר המלא הוא אחד הנפוצים ביותר מעגלי לוגיקה משולבים חיוניים . זהו מכשיר אלקטרוני בסיסי, המשמש לביצוע חיסור של שני מספרים בינאריים. במאמר הקודם כבר נתנו את התיאוריה הבסיסית של חצי תוספת & תוספת מלאה המשתמשת בספרות הבינאריות לצורך החישוב. כמו כן, החיסור המלא משתמש בספרות בינאריות כמו 0,1 לחיסור. המעגל של זה יכול להיות בנוי עם שערים לוגיים כגון OR, Ex-OR, NAND gate. התשומות של מחסר זה הן A, B, Bin והפלטים הם D, Bout.

מאמר זה נותן רעיון לתיאוריית גורע מלא הכולל את הנחות היסוד כמו מה שהוא מחסר, עיצוב עם שערי לוגיקה, טבלת אמת וכו '. מאמר זה שימושי לסטודנטים להנדסה שיכולים לעבור על נושאים אלה במעבדה המעשית של HDL.

מה זה מחסר?

חיסור הספרות הבינאריות יכול להיעשות בעזרת מעגל החיסור. זהו סוג אחד של מעגל לוגיקה משולב, המשמש לביצוע חיסור של שתי ספרות בינאריות כמו 0s ו- 1s. חיסור של ספרות בינאריות מ -0 ל -0 או 0 ל -1 אינו משנה את התוצאה, חיסור של 1 עד 1 יגרום ל -0 אך החיסור של 1 עד 0 צריך ללוות.

לדוגמא, מעגל החיסור הדו-ביטי כולל שתי כניסות כמו A & B ואילו הפלטים הם הבדל והשאלה. ניתן לבנות מעגל זה עם תוספים יחד עם ממירים הממוקמים בין כל קלט נתונים וכן קלט השאלה (Bin) של השלב הקודם של FA.

מחסירים מסווגים לשני סוגים כמו חצי מחסר וחיסור מלא. כאן אנו דנים בחיסור המלא.

מהו חיסור מלא?

זהו מכשיר אלקטרוני או מעגל לוגי המבצע חיסור של שתי ספרות בינאריות. זהו מעגל לוגי משולב המשמש באלקטרוניקה דיגיטלית. מעגלים משולבים רבים זמינים ב טכנולוגיית מעגלים משולבים כלומר מוסיפים, מקודדים, מפענחים ומולטיפקסרים. במאמר זה נדון בבנייתו באמצעות חצי גרעין וגם במונחים כמו טבלת האמת.

מחסר מלא

תכנון זה יכול להיעשות על ידי שני מחצאי מחצבים, הכוללים שלוש קלטות כגון מיניואנד, תת-הלוואה והלוואות, מעט לווה בין התשומות מתקבל מחיסור של שתי ספרות בינאריות ומופחת מזוג הבא של הסדר הגבוה יותר. סיביות, תפוקות כהפרש ולווה.

ה דיאגרמת בלוק חיסור מלאה מוצג להלן. החיסרון החשוב ביותר של חצי הגורע הוא שאיננו יכולים להרוויח קצת בורג בחיסור זה. בעוד שבעיצובו, אנו יכולים לעשות קצת לווה במעגל ויכול לחסר עם שני i / ps הנותרים. כאן A הוא מיניואנד, B הוא subtrahend ו- Bin מושאל פנימה. התפוקות הן Difference (Diff) & Bout (Borrow out). ניתן להשיג את מעגל החיסור השלם באמצעות שני מחצבי חיסור עם שער OR נוסף.

דיאגרמת מעגל חיסור מלאה עם שערי לוגיקה

ה תרשים מעגל של החיסור המלא באמצעות שער בסיסי s מוצג בתרשים הבלוקים הבא. מעגל זה יכול להיעשות עם שני מעגלי חצי גרעין.

במעגל החצי-מחסור הראשוני, הקלטים הבינאריים הם A ו- B. כפי שדנו במאמר הקודם של מחצית-החיסור, הוא יפיק שתי תפוקות, כלומר הפרש (Diff) ו- Lorrow.

מחסר מלא באמצעות שערי לוגיקה

ההפרש o / p של המחסר השמאלי ניתן למעגל חצי המגרע השמאלי. פלט Diff מסופק עוד יותר לקלט של מעגל החסר הימני. הצענו את ההשאלה קצת על פני ה- i / p האחרים של הבא חצי מעגל חיסור . שוב זה ייתן את Diff כמו גם את ההלוואות. התפוקה הסופית של חיסור זה היא Diff-output.

מצד שני, ההשאלה משני מעגלי המחסור מחוברת לשער ההיגיון OR. מאוחר יותר מאשר הוצאת לוגיקה של OR עבור שתי פיסות פלט של הגורע, אנו רוכשים את השאלה הסופית מתוך הגורם. ההשאלה האחרונה לציון ה- MSB (קצת משמעותי ביותר).

אם נצפה במעגל הפנימי של זה, אנו יכולים לראות שני מחצבי מחצית עם שער NAND ושער XOR עם שער OR נוסף.

טבלת האמת המחסנית המלאה

זֶה מעגל חיסור מבצעת חיסור בין שני ביטים, הכוללים 3 כניסות (A, B, ו- Bin) ושתי יציאות (D ו- Bout). כאן התשומות מציינות הלוואת מינונט, תת-הלוואה והלוואות קודמות, ואילו שתי התפוקות מסומנות כ- הלוואת o / p והפרש. התמונה הבאה מציגה את טבלת האמת של החסר המלא.

תשומות | תפוקות | |||

Minuend (A) | Subtrahend (B) | ללוות (סל) | הבדל (D) | ללוות (Bout) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

K-Map

הפשט של חיסור מלא של מפת K להפרש וללוות לעיל מוצג להלן.

המשוואות להבדל כמו גם ל Bin מוזכרות להלן.

הביטוי להבדל הוא,

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

הביטוי לשאלה הוא,

Bout = A'Bin + A'B + BBin

מדורג מעגל חיסור מלא

בעבר דנו בסקירה כללית של זה כמו בנייה, תרשים מעגלים עם שערי לוגיקה. אך אם ברצוננו לחסר שני מספרים נוספים של 1 סיביות, מעגל החיסור הזה מועיל מאוד לזרום מספרים של סיביות בודדות וגם לחסר יותר משני מספרים בינאריים. במקרים כאלה, נעשה שימוש במעגל מפלים מלא של מוספים בעזרת שער ההיגיון NOT. המרת המעגל ממספר מלא לחיסור מלא יכולה להיעשות בטכניקת השלמה של 2.

באופן כללי, הפוך את כניסות הסאב-טראנד עבור התוסף המלא באמצעות השער NOT, אחרת מהפך. על ידי הוספת Minuend (קלט לא הפוך) & Subtrahend (קלט הפוך) זה, ה- LSB (קלט נשיאה) של מעגל FA הוא 1, כלומר לוגיקה גבוהה אחרת אנו מפחיתים שתי ספרות בינאריות בטכניקת השלמה של 2. התפוקה של ה- FA היא ביט Diff & אם נהפוך את הביצוע, נוכל להשיג את ה- MSB אחרת לווה קצת. למעשה, אנו יכולים לתכנן את המעגל כך שניתן יהיה לראות את הפלט.

קוד Verilog

עבור החלק בקידוד, ראשית, עלינו לבדוק את הדרך המבנית של דוגמנות תרשים המעגל ההגיוני. את דיאגרמת הלוגיקה ניתן לבנות באמצעות שער AND, חצי מעגלי חיסור, ושילוב של שערי לוגיקה כמו AND, או, NOT, שערי XOR. כמו במודל מבני, אנו מסבירים מודולים שונים לכל סידור יסודי בסיסי. בקוד הבא ניתן להגדיר מודולים שונים לכל שער.

מודול זה מיועד לשער OR.

קלט: a0, b0

פלט: c0

לבסוף, נאחד את המודולים המדויקים של השער למודול יחיד. לשם כך, אנו משתמשים באינסטריזציה של המודול. כעת ניתן להשתמש באינסטיזציה זו ברגע שנרצה לשכפל מודול או פונקציה מדויקים עבור ערכות קלט מגוונות. ראשית, אנו מתכננים חצי חיסור ואז מודול זה משמש ליישום חיסור מלא. ליישום זה, אנו משתמשים בשער OR כדי לשלב את o / ps עבור המשתנה של Bout. ה קוד verilog עבור החסר המלא מוצג להלן

מודול or_gate (a0, b0, c0)

קלט a0, b0

פלט c0

הקצה c0 = a0 | b0

מודול הקצה

מודול xor_gate (a1, b1, c1)

קלט a1, b1

פלט c1

הקצה c1 = a1 ^ b1

מודול הקצה

מודול and_gate (a2, b2, c2)

קלט a2, b2

פלט c2

הקצה c2 = a2 & b2

מודול הקצה

מודול not_gate (a3, b3)

קלט a3

פלט b3

הקצה b3 = ~ a3

מודול הקצה

מודול חצי_גרע (a4, b4, c4, d4)

קלט a4, b4

פלט c4, d4

חוט x

xor_gate u1 (a4, b4, c4)

and_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

מודול הקצה

מודול full_subtractor (A, B, Bin, D, Bout)

קלט A, B, סל

פלט D, Bout

חוט p, q, r

מחצית_גורמת u4 (A, B, p, q)

מחצית_בוזר u5 (p, Bin, D, r)

or_gate u6 (q, r, Bout)

מודול הקצה

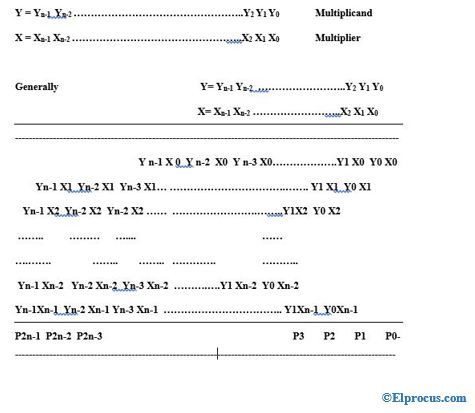

מחסר מלא באמצעות מכפלת 4X1

ביצוע החיסור יכול להיעשות בשיטת ההשלמה של השניים. לפיכך אנו דורשים שימוש בשער 1 XOR המשמש להפוך היפוך של 1 סיביות ולכלול אחד לסיבית נשיאה. תפוקת DIFFERENCE דומה לפלט SUM במעגל התוספת המלא אולם ה- BARROW o / p אינו דומה לתפוקת הנשיאה של התוספת המלאה אולם היא הפוכה ומחמיאה, כמו A - B = A + (-B) = השלמה של A + שניים של B.

העיצוב של זה באמצעות מכפל 4X1 מוצג בתרשים ההיגיון הבא. ניתן לבצע תכנון זה באמצעות השלבים הבאים.

מכפל 4X1

- בשלב 1 יש שתי תפוקות כמו Sub ו- Borrow. אז עלינו לבחור 2 מולטיפקסרים.

- בשלב 2 ניתן ליישם את טבלת האמת יחד עם מפות K

- בשלב 3, ניתן לבחור את שני המשתנים כשורת הבחירה שלך. לדוגמה, B & C הם במקרה זה.

שולחן האמת

ה טבלת האמת של החסר המלא מעגל באמצעות מכפל 4X1 כולל את הדברים הבאים

ל | ב | ג | תַת | לִלווֹת |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

מחסר מלא באמצעות מפענח

תכנון של חיסור מלא באמצעות 3-8 מפענחים יכול להתבצע באמצעות פלטים פעילים נמוכים. נניח שמפקד פועל באמצעות דיאגרמת ההיגיון הבאה. המפענח כולל שלוש כניסות ב-3-8 מפענחים. בהתבסס על טבלת האמת, אנו יכולים לכתוב את המינמטר עבור תפוקות ההבדל והשאלה.

מטבלת האמת שלעיל,

עבור הפונקציות השונות בטבלת האמת, ניתן לכתוב את המינוחים כ -1,2,4,7, וכמו כן, עבור ההשאלה ניתן לכתוב את המינוחים כ -1,2,3,7. המפענחים 3-8 כוללים שלוש כניסות וכן 8 יציאות כמו 0 עד 7 מספרים.

מפענח 3 עד 8

אם הקלט של החסר הוא 000, אז הפלט '0' יהיה פעיל ואם הקלט הוא 001, אז הפלט '1' יהיה פעיל.

כעת ניתן לקחת את הפלטים של הגורד מ 1, 2, 4 & 7 כדי לחבר אותו לשער NAND, ואז הפלט יהיה ההבדל. ניתן לחבר את היציאות הללו לשערי לוגיקה אחרים של NAND שבהם הפלט משתנה להלוואות.

לדוגמא, אם הקלט הוא 001, אז הפלט יהיה 1 שמשמעותו שהוא פעיל. כך שהפלט פעיל נמוך ואת הפלט ניתן להשיג משער NAND שנקרא פונקציית הבדל כמו פונקציית high ו- loan גם משתנה לגבוה. לכן אנו מקבלים את התפוקה המועדפת. אז סוף סוף, המפענח עובד כמו חיסור מלא.

יתרונות וחסרונות

ה היתרונות של החסר כלול את הבאים.

- תכנון החסר פשוט מאוד כמו גם יישום

- הפחתת כוח בתוך DSP (עיבוד אותות דיגיטלי)

- משימות חישוביות יכולות להתבצע במהירות גבוהה.

ה חסרונות של החסר כלול את הבאים.

- במחצית החיסור, אין תנאי לקבל קלט דמוי הלוואה מהשלב הקודם.

- מהירות החיסור יכולה להיות חלקית באמצעות העיכוב במעגל.

יישומים

חלק מה- יישומים של חיסור מלא כלול את הבאים

- אלה משמשים בדרך כלל עבור ALU (יחידת לוגיקה אריתמטית) במחשבים כדי להפחית כמעבד ו- GPU עבור יישומי גרפיקה כדי להקטין את קושי המעגל.

- מחסרים משמשים בעיקר לביצוע פונקציות חשבוניות כמו חיסור, במחשבונים אלקטרוניים כמו גם במכשירים דיגיטליים.

- אלה חלים גם על מיקרו-בקרים שונים לחיסור חשבון, טיימרים ומונה התוכנית (PC)

- משתמשים במחסנים במעבדים לחישוב טבלאות, כתובות וכו '.

- זה גם שימושי עבור DSP ומערכות מבוססות רשת.

- אלה משמשים בעיקר ל- ALU במחשבים להפחתה כמו CPU ו- GPU ליישומים גרפיים כדי להפחית את מורכבות המעגל.

- אלה משמשים בעיקר לביצוע פונקציות חשבוניות כגון חיסור במכשירים דיגיטליים, מחשבונים וכו '.

- חיסורים אלה מתאימים גם למיקרו-בקרים שונים עבור טיימרים, מחשב (מונה תוכניות) וחיסור חשבוני.

- אלה משמשים עבור מעבדים לחישוב כתובות, טבלאות וכו '.

- יישום זה בשערי לוגיקה כמו NAND & NOR יכול להיעשות בכל מעגל לוגיקה של חיסור מלא מכיוון ששני השערים NOR ו- NAND נקראים שערים אוניברסליים.

מהמידע שלעיל, על ידי הערכת התוספתן, החסר המלא באמצעות שני מעגלי חיסור חצי, וצורותיו הטבלאיות, ניתן להבחין כי Dout במחסור המלא דומה במדויק ל- Sout של המוסף המלא. הווריאציה היחידה היא ש- A (משתנה קלט) משלים במחסור המלא. לפיכך, ניתן להשיג את המעגל המלא-מלא למגרע מלא על ידי השלמת ה- i / p A רק לפני שהוא ניתן את שערי ההיגיון להפקת פלט סיביות ההשאלה האחרון (Bout).

על ידי שימוש בכל מעגל לוגיקה של חיסור מלא, ניתן ליישם חיסור מלא באמצעות שערי NAND וחסר מלא באמצעות ולא בשערים, מכיוון ששערי NAND ו- NOR מתייחסים כשערים אוניברסליים. הנה שאלה עבורך, מה ההבדל בין חצי מחסר לחיסר מלא?

![בניית מעגל ממיר באק פשוט [המרה מטה]](https://electronics.jf-parede.pt/img/3-phase-power/D0/build-a-simple-buck-converter-circuit-step-down-converter-1.jpg)