המונח VLSI מייצג 'טכנולוגיית שילוב בקנה מידה גדול מאוד' הכוללת תכנון מעגלים משולבים (IC) על ידי שילוב של אלפי טרנזיסטורים באופן הגיוני לשבב יחיד על ידי מעגלי לוגיקה שונים . מכשירי IC אלה מצמצמים בסופו של דבר את שטח המעגלים הכבושים בהשוואה למעגלים עם מכשירי IC רגילים. כוח חישובי וניצול שטח הם האתגרים העיקריים בתכנון VLSI. יישום פרויקטים של VLSI פותח קריירה מאתגרת ומבריקה עבור סטודנטים וחוקרים. חלק מהאזורים החדשים של VLSI הם מערך שערים לתכנות בשטח יישומים (FPGA), עיצובי ASIC ו- SOC. רשימה של כמה ממיזמי ה- VLSI מובאת להלן עבור אותם סטודנטים המחפשים ברצינות פרויקטים בתחום זה. מאמר זה דן בסקירה כללית על פרויקטים של VLSI המבוססים על FPGA, Xilinx, IEEE, Mini, Matlab וכו '. פרויקטים אלה מועילים מאוד לסטודנטים להנדסה, לסטודנטים למדעי הטכנולוגיה.

פרויקטים של VLSI לסטודנטים להנדסה

בהמשך נדון בפרויקטים של VLSI עם תקצירים לסטודנטים להנדסת אלקטרוניקה.

פרויקטים של VLSI

1). טרנספורמציה של גלי דיסקרטית על בסיס הרמת תלת מימד

פרויקט זה מסייע במתן תמונות מדויקות ביותר באמצעות קידוד של תמונה מבלי לאבד את הנתונים שלה. כדי להשיג זאת, תהליך זה מיישם מסנן הרמה בהתאם לתמורה של ארכיטקטורת VLSI של גלגלים נפרדים.

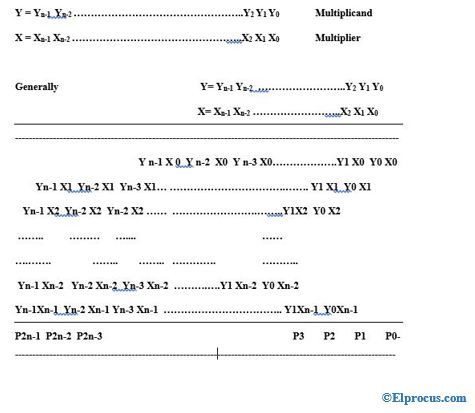

2). תכנון מכפיל SFQ עם 4 סיביות עם יעילות באמצעות חומרה מהירה

פרויקט זה משמש בעיקר ליישום מקודד תא מתוקן (MBE) עם בסיס SFQ בעל 4 סיביות מַכפִּיל . מכפיל זה מספק ביצועים טובים בהשוואה למקודד התא הקונבנציונאלי. פרויקט זה משמש בעיקר ביישומים של עיכוב קריטי.

3). מעבד קריפטוגרפיה המשמש בכרטיסים חכמים עם שטח יעיל

פרויקט זה משמש ליישום שלושה אלגוריתמי הצפנה הנתמכים על ידי מפתחות פרטיים וציבוריים המשמשים ב- כרטיס חכם יישומים לאספקת נתונים מאובטחים במיוחד תִקשׁוֹרֶת .

4). מכפיל במהירות גבוהה או בהספק נמוך עם שיטת דיכוי כוח זועמים

מערכת מוצעת זו מסננת את האותות הכוזבים חסרי התועלת של יחידות חשבון למניעת העברת נתונים מיותרת שאינה משפיעה על תוצאות המחשוב האחרונות. מערכת זו משתמשת בשיטת SPST עבור מכפילים כדי להשיג הספק נמוך והעברת נתונים במהירות גבוהה.

5). דחיסה ודחיסה של אלגוריתם נתונים ללא הפסד

פרויקט זה מיושם בעיקר עבור ארכיטקטורת חומרה דו-שלבית, בהתאם לתכונת האלגוריתם PDLZW (Parallel Dictionary LZW) וכן לאלגוריתם מסוג Adaptive Huffman המשמש הן ליישומים של דחיסת נתונים חסרת אובדן ודחיסה חסרת אובדן.

6). הארכיטקטורה של מפענח טורבו עם מורכבות נמוכה עבור רשתות WSN חסכוניות באנרגיה

המערכת המוצעת משמשת להפחתת צריכת האנרגיה הכוללת במהלך העברת נתונים של WSN באמצעות האלגוריתם המתפרק של LUT-Log-BCJR לפעולות ACS בסיסיות (Add Compare Select).

7). ארכיטקטורת VLSI להסרת רעש דחף של תמונה ביעילות

מערכת מוצעת זו שימשה בעיקר לשיפור איכות התמונה באופן חזותי למניעת הסיכויים להיפגם ברעש דחפים כדי להטמיע ארכיטקטורת VLSI יעילה בעזרת מסנן משמר קצה.

8). הארכיטקטורה של מעבד בזכרון המשמש לדחיסת מולטימדיה

מערכת מוצעת זו מספקת ארכיטקטורה מורכבת נמוכה עבור מעבד בזיכרון כדי לתמוך ביישומי מולטימדיה כלומר דחיסת תמונות, וידאו באמצעות יישום הוראה יחידה עצומה, מושגי נתונים מרובים ומילת הוראות.

9). טכניקת סינכרון תזמון עם קצב סמל למערכות OFDM אלחוטיות עם הספק נמוך

מערכת מוצעת זו שימשה בעיקר לשיפור פעולת ה- OFDM האלחוטית (חטיבת תדרים אורתוגונלית) רִבּוּב מערכת) באמצעות הפחתת העוצמה של כל פס הבסיס בעזרת שעון גֵנֵרָטוֹר עם בקר מתכוונן לתזמון מדגם פאזה ודינמי.

10). מצבר מבוסס יישום כוח נמוך ומהיר מכפיל במהירות גבוהה עם SPST Adder & Verilog

פרויקט זה משמש לעיצוב MAC בעל הספק נמוך ומהיר (מכפיל וצבר) באמצעות קבלת שיטת דיכוי שווא של כוח ב- MBE (מקודד תא שונה). על ידי שימוש בתכנון זה ניתן להימנע מפיזור הכוח של כל המיתוג.

11). תכנון ויישום מעבד רובוט על ידי הפעלת אנטי-התנגשות בטכנולוגיית RFID

המערכת המוצעת משמשת בעיקר להטמעת מעבד רובוט עם אנטי התנגשות כדי למנוע התנגשות פיזית של רובוטים בסביבה של רובוטים. אלגוריתם זה מיושם בעיקר באמצעות טכנולוגיית VHDL ו- RFID.

12). תכנון מעגל לוגי בהספק יעיל באמצעות שיטת Adiabatic

מערכת זו מדגימה את תכנון המעגלים הלוגיים ביעילות בשיטה אדיאבטית בהשוואה באמצעות תכנון CMOS קונבנציונאלי בעזרת מעגלים באמצעות שערים NAND & NOR . על ידי שימוש בשיטה האדיאבטית, ניתן להפחית את פיזור הכוח ברשת וכן למחזר את האנרגיה המאוחסנת בתוך קבל העומס.

3). מערכת הצפנה לשיפור מהירות המחשוב של המערכת

הכוונה העיקרית של פרויקט זה היא לשפר את אבטחת העברת הנתונים כדי לשפר את מהירות המחשוב על ידי יישום האלגוריתם של AES באמצעות FPGA. אז, סימולציה זו, כמו גם עיצוב מתמטי, יכולים להתבצע בעזרת קוד VHDL.

14). חסימת IP של AHM או אוטובוס מתקדם עם ביצועים גבוהים

פרויקט זה משמש בעיקר לתכנון אדריכלות של המתקדמים מיקרו-בקר אוטובוס (AMB) באמצעות AHBN (אוטובוס מתקדם עם ביצועים גבוהים). ניתן לתכנן פרויקט זה עם קוד VHDL על ידי יישום הבלוקים כמו master & save.

15). משדר מקלט רב-ממדי RF מבוסס DSM עם רב-ערוצי

מערכת זו שימשה בעיקר לתכנון ארכיטקטורת משדר ומקלט ורב-ערוצי RF מולטי-מצבים עם אפנן Delta-Sigma. מערכת מוצעת זו משתמשת בשפת VHDL כדי ליישם שני ארכיטקטורות.

16). רכז מתג הנוק-אאוט באמצעות מצב העברה אסינכרוני

באמצעות פרויקט זה ניתן לתכנן מתג נוקאאוט המבוסס על העברה אסינכרונית בעזרת כלים כמו VHS ו- VHDL. ניתן להשתמש במתג נוק-אאוט ברשתות של חבילות מעגלים וירטואליים, כמו גם ביישומים של הדאטגרמה.

17). סינתזה התנהגותית של מעגלים אסינכרוניים

פרויקט זה משמש בעיקר כדי לספק את טכניקת הסינתזה ההתנהגותית המשמשת למעגלים אסינכרוניים. שתי התבניות כמו הבלסה והיישומים האסינכרוניים הם האלמנטים העיקריים בתכנון.

18). עיצוב AMBA באמצעות בקר זיכרון תואם של AHB

פרויקט זה משמש לתכנון MC (בקר זיכרון) בהתאם ל- AMBA (אדריכלות אוטובוס Microcontroller Bus Advanced) לבקרת זיכרון המערכת באמצעות זיכרון ראשי כמו SRAM & ROM.

19). יישום תוספת עץ נשיאה

תוסף עץ נשיאה המבוסס על תכנון VLSI נקרא כתוספי הביצועים הטובים ביותר בניגוד לתוספים בינאריים רגילים. התוספות המיושמות על ידי פרויקט זה נפרשות על עץ, אבן קוגה ואבן קוגית דלילה.

20). CORDIC עיצוב מבוסס סיבוב של זווית קבועה

הרעיון העיקרי של מערכת מוצעת זו הוא הפיכת וקטורים באמצעות זוויות קבועות. זוויות אלה נחוצות למשחקים, רובוטיקה, עיבוד תמונה וכו '. באמצעות פרויקט זה ניתן להשיג סיבוב וקטורי באמצעות זוויות ספציפיות על ידי תכנון CORDIC (מחשב דיגיטלי לסיבוב סיבוב).

21). עיצוב מסנני FIR עם חשבון מבוזר של טבלת המראה

מערכת מוצעת זו משפרת בעיקר מסנן FIR ביצועים על ידי תכנונו באמצעות חשבון מבוזר של טבלת בדיקת תלת מימד במקום המכפיל. כך שניתן ליישם את העיצוב הזה באמצעות תוכנות כמו FPGA ו- Xilinx.

22). תפסים דחופים ומושכים עם מהירות גבוהה והספק נמוך

פרויקט זה משמש לביצוע תפסים פעימים חסכוניים באנרגיה וביצועים גבוהים המשמשים בעיקר למערכות VLSI באמצעות טופולוגיה חדשה. מכיוון שטופולוגיה זו תלויה בעיקר בשלב סופי של משיכת דחיפה המונעת באמצעות שני נתיבי חלוקה דרך מחולל דופק מותנה.

23). קודן אריתמטי VLSI אדריכלות ב- SPIHT

מערכת מוצעת זו משפרת את תפוקת שיטת הקידוד האריתמטי במחיצת קבוצות בעצים היררכיים (SPIHT) דחיסת תמונות עם הארכיטקטורה המהירה בהתאם ל- FPGA.

24). דיכוי רעש של אות א.ק.ג מבוסס על FPGA

פרויקט זה משמש להכיל את הרעש בתוך אותות א.ק.ג באמצעות שני פילטרים חציוניים עם 91 ו -7 גדלי נקודת מדגם בהתאמה. כך שניתן להגיע לתהליך זה באמצעות יישום ה- עיצוב FPGA מבוסס על קוד VHDL.

25). מעבד קנה מידה עם ביצועים גבוהים מבוסס VLSI בעלות נמוכה

פרויקט זה משמש ליישום אלגוריתם למעבד קנה מידה של תמונות המבוסס על VLSI עם פחות זיכרון וביצועים גבוהים. תכנון המערכת המוצע מכיל בעיקר שילוב של פילטר, שיטות דינמיות הניתנות להגדרה ושיתוף חומרה כדי להפחית את העלות.

26). מערך סיסטולי עיצוב אדריכלות ויישום ביעילות

הרעיון העיקרי של פרויקט זה הוא תכנון מודל חומרה המשמש למכפיל המערך הסיסטולי. מערך זה יכול לשמש בעיקר לביצוע כפל בינארי בעזרת פלטפורמת VHDL. ניתן ליישם את תכנון המערכת המוצע באמצעות תוכנת FPGA ו- Isim.

27). QPSK עיצוב וסינתזה באמצעות קוד VHDL

QPSK היא אחת משיטות האפנון העיקריות. שיטה זו משמשת ביישומי רדיו לוויני. ניתן ליישם טכניקת אפנון זו באמצעות שערי לוגיקה הפיכים. תכנון טכניקת QPSK יכול להיעשות בעזרת קוד ה- VHDL.

28). תכנון והטמעה של בקר SDRAM DDR במהירות גבוהה

המערכת המוצעת משמשת לתכנון בקר DDR SDRAM להעברת נתוני הפרץ בהתאם למהירות גבוהה לסינכרון נתונים אלה בין המעגלים של מערכת משובצת ו- DDR SDRAM. באמצעות שפת VHDL ניתן לפתח את הקוד.

29). 32 ומעבדי RISC מעבדים ומימוש

הרעיון העיקרי של פרויקט זה הוא יישום 32 סיביות RISC (מחשב להגדרת הוראות מופחת) בעזרת כלי כמו XILINK VIRTEX4. בפרויקט זה 16 ערכות הוראות מתוכננות בכל מקום בו ניתן לבצע כל הוראה במחזור CLK יחיד בשיטת הצנרת של חמש השלבים.

30). יישום גשר האוטובוסים בין AHB ו- OCP

המערכת המוצעת משמשת לתכנון גשר אוטובוסים בין שני פרוטוקולים כלומר משותף ותקן. פרוטוקולי התקשורת כמו AHB (Advanced High Performance Performance Bus) ו- OCP (Open Core Protocol) פופולריים מאוד המשמשים ביישומים של SoC (מערכת שבב) .

רעיונות לפרויקטים של VLSI לסטודנטים להנדסה

רשימת פרויקטי VLSI המבוססים על FPGA, MatLab, IEEE, ומיני פרויקטים לסטודנטים להנדסה מפורטים להלן.

פרויקטים של VLSI לסטודנטים מ 'טק

רשימת פרויקטים של VLSI המבוססת על סטודנטים מ 'טק כוללת את הדברים הבאים.

- יעיל שטח ואמין מבוסס RHBD מבוסס תאי זיכרון I0T המשמשים ליישומי חלל

- גלאי פאזה עם חצי קצב רב-מפלסי המשמש למעגלי CLK ושחזור נתונים

- משווה עם הספק נמוך ומהירות גבוהה המשמש ליישומים מדויקים

- מתרגם רמת מתח מגודרת עם מכפלת ביצועים גבוהה ומשולבת

- Adder Ternary מבוסס CNTFET עם ביצועים גבוהים

- עיצוב משווה גודל בהספק נמוך

- תכנון שער סף לוגי עם מצב נוכחי לניתוח עיכוב

- עיצוב מפענחי קו מעורב-לוגי עם הספק נמוך וביצועים גבוהים

- עיצוב קונבנציונאלי לישון לציון לישון

- מפלס מתח מתח ליישומי אספקה כפולה במהירות גבוהה וחסכונית בחשמל

- הספק נמוך & מתח נמוך זנב כפול תכנון וניתוח

- עיצוב כפכף המבוסס על הדופק המופעל באמצעות צריכת חשמל נמוכה בשיטת הזנת אותות

- תכנון מעגלים יעיל המבוסס על FETs ניתנים להגדרה מחדש של Runtime

- עיצוב משווה גודל בהספק נמוך

- ניתוח עיכוב של עיצובי שער לוגי עם סף מצב נוכחי

ה פרויקטים מסוג VLSI מבוססי FPGA לסטודנטים להנדסה ו פרויקטים מיני של CMOS VLSI לעיצוב מפורטים להלן.

- SEU מעגלים קשוחים עיצוב ואפיון עבור FPGA מבוסס על SRAM

- A CMOS קומפקטי מבוסס CMOS היברידי LUT עיצוב & יישום פוטנציאלי המשמש FPGA

- יישום מבוסס חיישן אולטרה סאונד של FPGA למדידת מרחק

- יישום FPGA למכפיל תא עם Spartan6 FPGA

- טרנספורמציה של גלי גלידה בדידים המבוססת על הרמה באמצעות Spartan3 FPGA

- בקר ARM ברובוטיקה באמצעות FPGA

- UP מבוסס FPGA עם רב ערוצים

- דיכוי רעש אותות א.ק.ג באמצעות FPGA

- יישום FPGA מבוסס UTMI ושכבת פרוטוקול USB 2.0

- יישום מסנן חציוני עם Spartan3 FPGA

- יישום מבוסס אלגוריתם AES של FPGA

- מערכת התראות אבטחה המבוססת על PIC ליישום FPGA עם Spartan 3an

- יישום FPGA לתכנון הבקר למערכות חישה מרחוק

- ערכת עיבוד תמונה של FPGA באמצעות סינון תמונות של לינארית ומורפולוגית

- יישום תמונות היתוך רפואי מבוסס FPGA על ידי Spartan3

רשימת פרויקטים מיני של VLSI המשתמשים בקוד VHDL כולל את הדברים הבאים.

- משווה במהירות גבוהה באמצעות VLSI

- מכפיל של נקודה צפה באמצעות VLSI

- המרה מבוססת VLSI של בינארי לאפור

- מסנן דיגיטלי

- CLK Gating מבוסס על VLSI

- מכפיל וודי

- CMOS FF באמצעות VLSI

- הארכיטקטורה של מעבד מקבילי המשתמש ב- VLSI

- Adder מלא מבוסס VLSI

- תכנון זיכרון DRAM / Dynamic Random Access מבוסס על VLSI

- פריסת SRAM המבוססת על VLSI

- מעבד אותות דיגיטלי מבוסס VLSI

- מרבב מבוסס VLSI

- תכנון יחידת MAC המבוססת על VLSI

- מבדיל מבוסס VLSI

- FFT מבוסס VFT או טרנספורמציה מהירה יותר

- הארכיטקטורה של טרנספורמט קוסינוס דיסקרטי המבוססת על VLSI

- עיצוב מכפיל 16 סיביות באמצעות VLSI19

- תכנון מבוסס VLSI של מאגר FIFO

- מאיץ מהיר מבוסס VLSI

פרויקטים של VLSI המשתמשים ב- MATLAB & Xilinx

רשימת פרויקטים של VLSI המבוססים על פרויקטים של MATLAB ו- VLSI המשתמשים ב- Xilinx כוללת את הדברים הבאים.

- תכנון וניתוח מודמים של CDMA עם MATLAB

- עיצוב מסנני FIR באמצעות VHDL בניתוח מבוסס FPGA ו- MATLAB

- ModelSim & Matlab או סימולינק מבוסס סימולציה של מערכת להנדסת רכב

- תוספים מבוססי Xilinx כמו Ripple Carry & Carry Skip

- יחידת חשבון המבוססת על 32 סיביות נקודה צפה

- ALU מבוסס נקודה צפה

- מעבד RISC מבוסס על 32 סיביות

- יכולות התפתחות של קוד אורתוגונלי

- מכונות אוטומטיות מבוססות Xilinx ו- Verilog

- תוספי קידומת מקבילים מבוססי Xilinx עם 256 סיביות

- פרוטוקול לאימות הדדי באמצעות Xilinx

- מבנה גישה באמצעות מחזור יחיד לבדיקת לוגיקה באמצעות Xilinx

- UTMI & Protocol Layer מבוסס USB2.0 באמצעות Xilinx

- תצורה של דחיסת נתונים ושחרור לחץ באמצעות Xilinx FPGA

- XPP- מבוססות BIST ו- Spartan מבוססות Xilinx 4000

- מסנן IIR מבוסס על MATLAB & VLSI

- מסנן FIR באמצעות MATLAB

פרויקטים של IEEE

ה רשימת פרוייקטים של IEEE VLSI מופיע להלן.

- מערכת אוטומציה ביתית אלחוטית מבוססת VLSI באמצעות Bluetooth

- הסרת רעש דחף בתוך תמונה באמצעות ארכיטקטורה יעילה של VLSI

- הארכיטקטורה של מעבד בזכרון לדחיסת מולטימדיה

- ניטור מערכת הטמפרטורה באמצעות ענן ו- IoT

- יישום מערכת OFDM עם IFFT & FFT

- עיצוב קוד יישום והטמעת קוד באמצעות Verilog

- זיהוי טביעות אצבע מבוסס VHDL באמצעות מסנן גאבור

- פונקציות חשבון מחדש עם ROM בהתאם לגישות הקירוב

- ניתוח יעילות גבוהה וביצועים בצפיפות נמוכה של מפענח קוד בדיקת זוגיות ביישומים בעלי צריכת חשמל נמוכה

- ארכיטקטורות FFT עם הזנה של Radix-2k עם צינור

- כפכפים עיצוב ליישומי VLSI באמצעות טכנולוגיית CMOS עם ביצועים גבוהים

- עיצוב מסנני FIR עם טבלת בדיקה לפי חשבון מבוזר

- מעבד קנה מידה תמונה בעלות נמוכה ומשופרת על ידי VLSI

- ASIC יישום ועיצוב של מקודד ומפענח טורבו מתקדם עם 3GPP LTE

- תפסים דחופים ומושכים עם כוח נמוך ומותנים במהירות גבוהה

- סריקה משופרת בבדיקת סריקה בהספק נמוך

- קודן אריתמטי VLSI אדריכלות עבור SPIHT

- יישום VHDL ל- UART

- וסת מתח מבוסס VLSI עם נשירה נמוכה

- עיצוב ADC פלאש עם תכנית משווה משופרת

- עיצוב מכפיל כוח הספק נמוך עם סגנון לוגי מורכב של עיכוב קבוע

- משווה זנב כפול עם ביצועים גבוהים והספק נמוך

- מערכת אחסון פלאש עם ביצועים גבוהים בהתאם למאגר כתיבה וזיכרון וירטואלי

- צריכת חשמל נמוכה FF המבוססת על גישת ערימה מנומנמת

- אופטימיזציה של צריכת חשמל LFSR עבור BIST בהספק נמוך מיושם ב- HDL

- תכנון ויישום מכונות אוטומטיות עם Verilog HDL

- תכנון מצברים המבוסס על הדור של דפוס בעל משקל 3 עם LP-LSFR

- מפענח ריד-סולומון עם מהירות גבוהה ומורכבות נמוכה

- טכניקת עיצוב מכפיל דדה מהירה יותר

- מקלט מבוסס רמה דיגיטלית על בסיס הדמולציה

- יצירת דפוס בדיקה עם תוכניות BIST

- יישום אדריכלות VLSI עם צינור מהיר

- תכנון פרוטוקול OCP באוטובוס על שבב באמצעות פונקציות של אוטובוסים

- גלאי תדרים שלב ותכנון משאבת מטען המשמש לולאה נעולה שלב גבוהה

- זיכרון מטמון ועיצוב בקר מטמון עם VHDL

- יישום מבוסס ASTRAN של מדחסי תוספת 3-2 ו -4-2 הספקים נמוכים

- מערכת חיוב חשמל בתשלום מראש באמצעות עיצוב על שבב

- יישום חפיפה באמצעות תא לוגיקה וניתוח הכוח שלו

- נשא מבט קדימה עם ניתוח ביצועי ביטים שונים באמצעות VHDL

- עיצוב שכבת קישור נתונים עם MAC Wi-Fi פרוטוקולים

- יישום FPGA לפרוטוקול אימות הדדי עם חשבון מודולרי

- הפקת אותות PWM באמצעות FPGA ומחזור עבודה משתנה

פרויקטים בזמן אמת

רשימת פרויקטים בזמן אמת של VLSI כולל בעיקר פרויקטים מיני VLSI המשתמשים בקוד VHDL ופרויקטים של תוכנת VLSI לסטודנטים להנדסת ECE.

- שילוב פרגמטי של מטמון שורה של SRAM בארכיטקטורת DRAM תלת-ממדית הטרוגנית באמצעות TSV

- טכניקת בדיקה עצמית מובנית לאבחון תקלות עיכוב במערכי שערים הניתנים לתכנות בשטח

- תכנון ASIC של מכפיל מורכב

- יישום VLSI בעלות נמוכה להסרת יעיל של רעש דחפים

- מבוסס FPGA חלל וקטור PWM בקרת IC עבור כונן מנוע אינדוקציה תלת פאזי

- יישום VLSI של מתאם אוטומטי ואלגוריתם קורדי עבור WLAN מבוסס OFDM

- חילוץ דרך אוטומטי באמצעות תמונות לוויין ברזולוציה גבוהה

- תכנון VHDL לפילוח תמונות באמצעות פילטר גאבור לזיהוי מחלות

- ארכיטקטורת מפענח טורבו מורכבת נמוכה לרשתות חיישנים אלחוטיות חסכוניות באנרגיה

- שיפור יכולות ההתמוטטות של הקוד האורתוגונאלי באמצעות יישום FPGA

- תכנון והטמעה של ALU Point Floating

- תכנון קורדי לזווית סיבוב קבועה

- קודי מוצר ריד-סולומון ליישום בקר NAND פלאש על שבב FPGA

- שיפור SRAM סטטיסטי של קריאת גישה באמצעות מעגלי קיבול שליליים

- ניהול כוח של ממשקי רשת MIMO במערכות ניידות

- תכנון תקן הצפנת נתונים להצפנת נתונים

- תוסף נשיאה בביצוע יעיל עם מתח נמוך ויעיל

- סינתזה והטמעה של UART באמצעות קודי VHDL

- ארכיטקטורות משופרות ליחידת הוצאה של נקודה צפה ממוזגת

- משדר דיגיטלי מבוסס 1 FPGA משדר דיגיטלי המעסיק אפנון דלתא-סיגמא עם פלט RF עבור SDR

- מיטוב השימוש בחיפוש שרשרת במפענח BCH להעברת שיעורי שגיאה גבוהים

- תכנון דיגיטלי של משדר DS-CDMA באמצעות Verilog HDL ו- FPGA

- תכנון ויישום של אדריכלות מערך סיסטולית יעילה

- אלגוריתם למידה של רובוטים דינמיקה מבוססי VLSI

- תכנון יחידת פונקציונלית רב-תכליתית מולטימדיה תוך שימוש בטכניקת דיכוי הכוח הזעם

- תכנון גשר אוטובוסים בין AHB ל- OCP

- סינתזה התנהגותית של מעגלים אסינכרוניים

- אופטימיזציה מהירה של מפענח Viterbi שונה המבוסס על FPGA

- יישום ממשק I2C

- מכפיל במהירות גבוהה / בהספק נמוך באמצעות טכניקת דיכוי כוח זעם מתקדמת

- הידוק מתח אספקה וירטואלי של מעגלים מגודרים כוח להפחתת דליפה פעילה ואמינות תחמוצת שער

- ערוץ יעיל כוח יעיל מבוסס FPGA עבור רדיו המוגדר על ידי תוכנה

- ארכיטקטורת VLSI ו- FPGA אבות טיפוס של מצלמה דיגיטלית לאבטחת תמונה ואימות

- שיפור מבצע של רובוט מקורה

- תכנון והטמעה של רשת חלופות ON-Chip למערכת מרובת-מעבדים

- שיטת סינכרון תזמון קצב-סימבול למערכות OFDM אלחוטיות בעלות הספק נמוך

- בקר DMA (גישה ישירה לזיכרון) באמצעות VHDL / VLSI

- ניתן להגדיר מחדש FFT באמצעות ארכיטקטורה מבוססת CORDIC עבור מקלטים MIMI-OFDM

- טכניקת דיכוי כוח זועמים ליישומי מולטימדיה / DSP

- היעילות של קודי BCH בסימני מים דיגיטליים

- בקר כפול נתונים SD-RAM בקר

- הטמעת מסנן Gabor לזיהוי טביעות אצבע באמצעות Verilog HDL

- תכנון סולם ננומטר מעשי מיותר באמצעות ספריית תאים סטנדרטית מודעת למיותר משופר באמצעות קצב הכנסה אחד

- אלגוריתם דחיסת נתונים ודחיסת נתונים ללא הפסד וארכיטקטורת החומרה שלו

- מסגרת לתיקון שגיאות רכות מרובות ביט

- דחיסת נתוני בדיקה יעילה מבוססת Viterbi

- יישום בלוקים FFT / IFFT עבור OFDM

- דחיסת תמונה מבוססת גלי על ידי קידוד פרוגרסיבי של VLSI

- יישום VLSI של מכפיל צינור מלא פחות אדריכלות DCT / IDCT דו-ממדית עבור Jpeg

- הדמיית תקלות מבוססת FPGA של מעגלים רצפים סינכרוניים

לפיכך, מדובר בסך הכל ברשימת פרויקטי VLSI להנדסה, סטודנטים למדעי הטכנולוגיה המסייעים בבחירת נושא הפרויקט שלהם בשנה האחרונה. לאחר שביליתם את זמנכם היקר בזמן שעברתם את הרשימה הזו, אנו מאמינים שיש לכם רעיון טוב למדי לבחור את נושא הפרויקט שבחרתם מרשימת הפרויקטים של VLSI, ומקווים שיש לכם מספיק ביטחון לקחת נושא כלשהו רשימה. לפרטים נוספים ועזרה בפרויקטים אלה, תוכלו לכתוב לנו במדור ההערות המופיע להלן. הנה שאלה עבורך, מה זה VHDL?

אשראי צילום

- פרויקטים של VLSI מאת סט-טק

![בניית מעגל ממיר באק פשוט [המרה מטה]](https://electronics.jf-parede.pt/img/3-phase-power/D0/build-a-simple-buck-converter-circuit-step-down-converter-1.jpg)